- 您现在的位置:买卖IC网 > Sheet目录511 > SI5040-D-GM (Silicon Laboratories Inc)IC TXRX XFP 10GBPS 32LGA

�� �

�

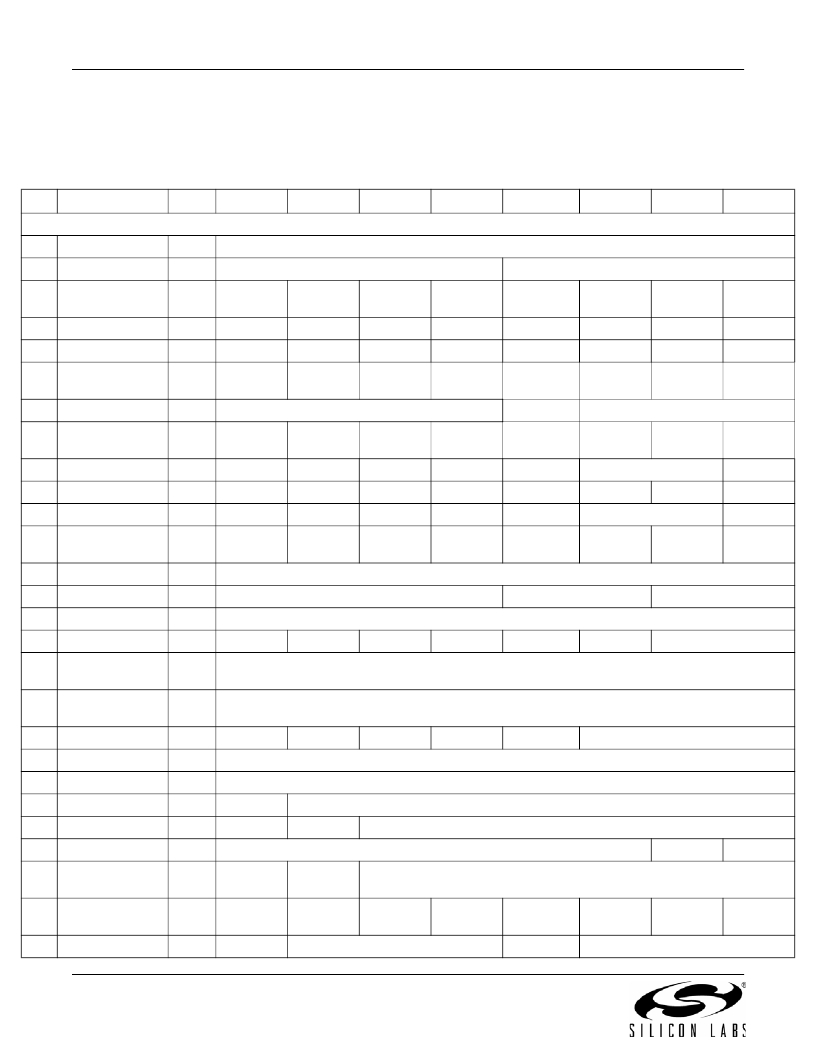

Si5040�

�13.� Si5040� Register� Summary�

�Any� reserved� bits� listed� in� the� table� below� or� reserved� registers� (23,� 54–55,� 58–76,� 78–83,� 86–97,� 99–105,� 110–�

�130,� 140–144,� 148–151,� 182–183,� 185–204,� 206–225,� and� 227–255)� must� not� be� written� to� a� non-default� value.�

�All� reserved� bits� have� the� default� values� shown� below.�

�Reg�

�Name�

�Default�

�Bit� 7�

�Bit� 6�

�Bit� 5�

�Bit� 4�

�Bit� 3�

�Bit� 2�

�Bit� 1�

�Bit� 0�

�Receiver�

�0�

�Part� Identifier�

�40h�

�Identifier[7:0]�

�1�

�Part� Identifier�

�30h�

�Revision[3:0]�

�Identifier[3:0]�

�2�

�ChipConfig1�

�58h�

�losOpen�

�intOpen�

�intEnable�

�spiOpen�

�Reserved�

�lineside-�

�XFILoop-�

�refClkFreq�

�Drain�

�Drain�

�Drain�

�Loopback�

�back�

�3�

�4�

�5�

�RxChipConfig2�

�RxintMask�

�RxintStatus�

�0h�

�0h�

�0h�

�Reserved�

�Reserved�

�Reserved�

�Reserved�

�refLOS�

�refLOS�

�Reserved�

�LOS�

�LOS�

�Reserved�

�LOL�

�LOL�

�Reserved�

�fifoErr�

�fifoErr�

�Reserved�

�tpErrAlarm�

�tpErrAlarm�

�Reserved�

�tpSyncLos�

�tpSyncLos�

�RxPdn�

�sqmAlarm�

�sqmAlarm�

�(Sticky� Bits)�

�6�

�RxCmuConfig�

�40h�

�cmuBandwidth[3:0]�

�Reserved�

�Reserved�

�7�

�RxConfig�

�15h�

�Reserved�

�lolOnLOS�

�ltrOnLOS�

�CDRLT-�

�uselolMode�

�lolMode�

�ltr�

�rxRefclkEn�

�DATA�

�8�

�RxCalConfig�

�0h�

�Reserved�

�Reserved�

�Reserved�

�Reserved�

�hardRecal�

�VCOCAL[1:0]�

�swReset�

�9�

�RxAlarmStatus�

�0h�

�Reserved�

�refLOS�

�LOS�

�LOL�

�fifoErr�

�tpErrAlarm�

�tpSyncLos�

�sqmAlarm�

�10�

�RxLosCtrl�

�1h�

�Reserved�

�Reserved�

�Reserved�

�Reserved�

�sqmLosEn�

�dLosEn[1:0]�

�aLosEn�

�11�

�RxLosStatus�

�0h�

�Reserved�

�Reserved�

�Reserved�

�sqmLos�

�dLOSlast-�

�dLOS�

�aLOS�

�LOS�

�Trigger�

�12�

�aLosThresh�

�Fh�

�aLOSThresh[7:0]�

�13�

�15�

�aLosThresh2�

�peakDet�

�70h�

�0h�

�aLosHyst[3:0]�

�peakDet[7:0]�

�Reserved�

�aLosThresh[1:0]�

�16�

�peakDet�

�0h�

�Reserved�

�Reserved�

�Reserved�

�Reserved�

�Reserved�

�Reserved�

�peakDet[1:0]�

�17�

�RxdLosAssert-�

�5h�

�RxdLosAssertThresh[7:0]�

�Thresh�

�18�

�RxdLos�

�60h�

�RxdLosClearThresh[7:0]�

�ClearThresh�

�20�

�sliceConfig�

�11h�

�Reserved�

�Reserved�

�Reserved�

�Reserved�

�Reserved�

�sliceEn[2:0]�

�21�

�22�

�sliceLvl�

�sliceLvl�

�0h�

�0h�

�sliceLvl[7:0]�

�sliceLvl[15:8]�

�24�

�RxphaseAdjust�

�0h�

�Reserved�

�RxphaseAdjust[6:0]�

�25�

�RxSqmValue�

�N/A�

�Reserved�

�Reserved�

�RxSqmValue[5:0]�

�26�

�RxSqmConfig�

�29h�

�RxSqmThresh[5:0]�

�Reserved�

�Reserved�

�27�

�RxSqmDeassert-�

�Fh�

�Reserved�

�Reserved�

�RxSqmDeassertThresh[5:0]�

�Thresh�

�28�

�RxdPathConfig�

�2h�

�Reserved�

�dinvert�

�clkOnLOS�

�SquelchOn-� SquelchOn-�

�Squelch�

�FIFOAu-�

�FIFOReset�

�RxLOL�

�RxLOS�

�toReset�

�29�

�RxtpSel�

�0h�

�tpChkInvert�

�tpChkSel[2:0]�

�tpGenInvert�

�tpGenSel[2:0]�

�40�

�Rev.� 1.3�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SI5402DC-T1-GE3

MOSFET N-CH D-S 30V 1206-8

SI5403DC-T1-GE3

MOSFET P-CH 30V 6A 1206-8

SI5432DC-T1-GE3

MOSFET N-CH 20V 6A 1206-8

SI5440DC-T1-GE3

MOSFET N-CH D-S 30V 1206-8

SI5441DC-T1-GE3

MOSFET P-CH D-S 20V 1206-8

SI5443DC-T1-GE3

MOSFET P-CH D-S 20V 1206-8

SI5468DC-T1-GE3

MOSFET N-CH D-S 30V 1206-8

SI5475BDC-T1-GE3

MOSFET P-CH 12V 6A 1206-8

相关代理商/技术参数

SI5040-D-GMR

制造商:Silicon Laboratories Inc 功能描述:XFP Transceiver 1TX 1RX 10Gbps 32-Pin LGA T/R 制造商:Silicon Laboratories Inc 功能描述:XFP TRANSCEIVER, PB FREE - Tape and Reel 制造商:Silicon Laboratories Inc 功能描述:IC TXRX XFP 10GBPS 32LGA

SI5040-D-ZM2

制造商:Silicon Laboratories Inc 功能描述:XFP TRANSCEIVER, PB FREE - Rail/Tube

SI5040-D-ZM6

制造商:Silicon Laboratories Inc 功能描述:XFP TRANSCEIVER - Rail/Tube

SI5040-D-ZM7

制造商:Silicon Laboratories Inc 功能描述:XFP TRANSCEIVER, PB FREE - Rail/Tube

SI5040-EVB

功能描述:BOARD EVAL SI5040 RoHS:否 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板

SI5041-B-GM

制造商:Silicon Laboratories Inc 功能描述:10G DUAL CDR (REV B FOR PROTOTYPE ONLY, REV C FOR P - Rail/Tube

SI5041-B-GMR

制造商:Silicon Laboratories Inc 功能描述:10G DUAL CDR (REV B FOR PROTOTYPE ONLY, REV C FOR P - Tape and Reel

SI5041-C-GM

制造商:Silicon Laboratories Inc 功能描述:10G DUAL CDR, LEAD FREE - Rail/Tube